The development of the storage industry is inseparable from the analysis of data generation. According to data provided by the third-party research institution IDC in 2018, the global data generation is expected to reach 175 zettabytes (ZB) by 2025. However, in Q4 of 2023, IDC revised the data, increasing the global data generation forecast for 2025 to 181 ZB. This implies that the compound annual growth rate (CAGR) of global data generation from 2024 to 2027 will be 22.4%.

Another data point from IDC suggests that by 2027, the total global data generation could reach 291 ZB. Not every piece of data is useful, so the portion that is preserved is less than 10%. Yet, even this 10% requires various forms of storage media to record and ultimately be presented to everyone.

Recently, Yangtze Memory Technologies (YMTC) showcased a series of products and technical solutions. The new generation of QLC 3D NAND flash memory, with the internal codename "X3-6070," boasts exceptionally high quality, capable of meeting the application needs across enterprise, consumer, and embedded scenarios.

Its IO interface speed has reached 2400MT/s, a significant 50% increase compared to the previous generation's 1600MT/s, while both read and write speeds have nearly doubled.

What's even more remarkable is its reliability and lifespan. The P/E (program/erase) cycle can astonishingly reach 4000 times, which is four times that of the previous generation's product.

Advertisement

It's important to note that conventional MLC (multi-level cell) flash memory can only achieve around 3000 P/E cycles, while TLC (triple-level cell) flash memory initially only managed 100-150 cycles, and even after maturing, it only reached about 1000 cycles. The enterprise-grade enhanced version also only achieves around 3000 cycles.

According to YMTC staff, their QLC flash memory can achieve 4000 P/E cycles, partly due to the unique Xtacking architecture and also as a result of the maturation of processes and technology.

Of course, not all QLC flash memory reaches such a high standard; it is limited to enterprise-grade products and depends on the yield rate. The consumer-grade can reach up to around 2000 cycles at most.

In terms of specific products, the situation will also vary, depending on product positioning and design, and considering factors such as write amplification. For example, YMTC's first self-branded QLC product, the Zhitai Ti600, is estimated to have around 600 cycles.

In the OEM (Original Equipment Manufacturer) field, YMTC's next-generation PC41Q will introduce QLC, which can be used in laptops, desktops, all-in-ones, and more.It supports PCIe 4.0 x4, NVMe 1.4, with read and write bandwidth of 5.5GB/s, dynamic power consumption below 4W, PS4 standby power consumption below 2mW, and boasts high reliability and data retention capabilities comparable to TLC, with an average time between failures reaching 2 million hours, capable of stably retaining data for up to a year in an environment of 30°C.

In addition to QLC flash memory, Yangtze Memory also showcased enterprise-level SSDs and embedded UFS/eMMC products.

3D NAND Technology Roadmap Update

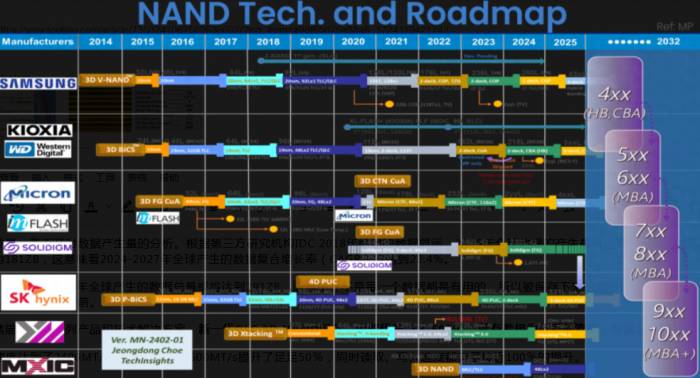

Recently, TechInsights updated and reviewed the 3D NAND industry roadmap. It discussed the 3D NAND technology roadmaps of major manufacturers, including Samsung, Kioxia/Western Digital, Micron, and SK Hynix/Solidigm.

TechInsights stated that Samsung changed the 1 deck structure to a 2-deck architecture in V7 and altered the 2D array-peripheral design to a cell-on-peripheral (COP) integration. Samsung has launched the V8 236L 1Tb TLC product, which is their second COP architecture.

Last year, TechInsights commented that they might add a node below 300 layers, such as an n+1 280-layer or 290-layer product. Samsung now has the 280L V9 COP V-NAND. Furthermore, Samsung added a 133L V6 Prime version, known as V6P, for the 990 EVO. The 133-layer is a single deck without a COP structure. The total gate count is 133, with the active wordline count increasing from 128 to 133, and the speed increasing to 1600 MT/s, with two sub-planes on each plane in a 512 Gb die. The next generation V10 will adopt a hybrid bonding technology similar to products like Kioxia's 218L CBA.

Kioxia and Western Digital have maintained the BiCS architecture, with most of the products on the market still being the fifth generation 112 L. BiCS6 162L is likely a risky product and may not last long. Kioxia has indicated that they will skip the seventh generation of BiCS, and the upcoming eighth generation of BiCS will have 218 layers, while the BiCS in development will have 284 layers. Both 218-layer and 284-layer will adopt dual-wafer hybrid bonding technology, and if the development of the 3xx-layer goes smoothly, the 284-layer might be skipped again.

Micron transitioned from FG CuA to CTF CuA integration in their 128 layers, and since then, they have been ahead of other competitors in launching 176-layer and 232-layer products to the market. Like Samsung's 280L, Micron is developing a seventh-generation product below 300 layers. Micron might skip the 300-layer product and directly jump to a 400-layer product.

The Four Basic Technologies to Increase 3D NAND Flash Memory Storage Density3D NAND is a type of non-volatile storage technology (NVM Non-Volatile Memory), which is a category of memory devices.

Currently, 2D NAND, also known as planar NAND, has reached the limit of its capacity development. 3D NAND was developed to overcome the capacity limitations of 2D NAND. The 3D NAND architecture can expand to higher densities without sacrificing data integrity.

Unlike 2D NAND, which stacks storage cells horizontally, 3D NAND uses multi-layer vertical stacking to achieve higher density, lower power consumption, better durability, faster read and write speeds, and lower costs. Due to the packaging of so many vertical cells into smaller width and length dimensions, 3D NAND has a larger capacity than 2D NAND at the same width and length dimensions.

The methods for increasing the density of 3D NAND flash memory are changing. This is because the fundamental technologies that support traditional high-density technologies are expected to reach their limits in the near future. The introduction and transformation of new foundational technologies are likely to become more common between 2025 and 2030.

Since the commercial production of 3D NAND flash memory began in 2013, the storage density has been continuously increasing at a rate of approximately 1.41 times per year. Looking at prototype silicon chips displayed at the international conference ISSCC, the storage density was 0.93 Gbit per square millimeter in 2014, but it will reach 28.5 Gbit per square millimeter by 2024. In a simple comparison, the storage density has increased by 30.6 times in 10 years.

So far, the storage density of 3D NAND flash memory has been mainly increased by adopting four basic technologies. These are "layering," "multi-level cell (MLC)," "layout change (monolithic layering of storage cell arrays and CMOS peripheral circuits)," and "miniaturization (reducing lateral dimensions)."

Comment Box